# Designing embedded **Ethernet devices**

By

Dr. Martin Moerz

Revision One Engineering GmbH

# **DISCLAIMER**

Dacom West GmbH (Dacom) sells commodity on basis and in scope of Dacom General Terms and Conditions of Supply and Payment. We are not able to recognize opposing terms and conditions.

As a trader Dacom makes no express warranties and is not liable for injuries, damages and losses under a duty of implied or statutory warranties, if there is no fault on our side. This applies to all product specifications, all product information and patent infringements.

All information provided by Dacom is believed to be correct. But please take into consideration, that Dacom as your dealer is not producer of the delivered items.

Therefore Dacom shall neither be liable to the product addressee nor to any third party, with the exception of a statutory strict liability, for any damages whatsoever if there is no wilful or negligent act on side of Dacom. This applies to damages arising out of faulty products as well as to damages arising out of faulty information, for example in data sheets or catalogues. By rendering technical services we are liable for losses caused by us in case of intentional and reckless conduct.

Before designing products delivered by Dacom into a system we strongly recommend to consult Dacom or the manufacturer.

Before using any information or products provided by Dacom in a system we strongly recommend to consult Dacom or the manufacturer. This is particulary applicable, if the safety of the product application is concerned, i.e. if the danger of bodily injuries, property damages or financial losses cannot be excluded with sufficient certainty.

In scope of a Yes-No-Don't-know-system we would be glad to advise you in terms of application. Accordingly, you are requested to verify that our data sheets and other publications you possess are current and up to date.

The user agrees to this disclaimer by using the information including this disclaimer.

# Inhalt

| 1 |    | Intr | odu    | ction                                         | . 5 |

|---|----|------|--------|-----------------------------------------------|-----|

| 2 |    | Αlα  | ook a  | at the physical layer                         | . 6 |

|   | 2. | 1    | Ove    | erview                                        | . 6 |

|   | 2. | 2    | The    | Media Dependent Interface                     | . 7 |

|   |    | 2.2  | .1     | Physical connection                           | . 7 |

|   |    | 2.2  | .2     | Electrical safety                             | . 8 |

|   |    | 2.2  | .3     | Electromagnetic Interference                  | 10  |

|   |    | 2.2  | .4     | 10Base-T and 100Base-TX in particular         | 11  |

|   | 2. | 3    | The    | Media Independent Interface                   | 20  |

|   |    | 2.3  | .1     | The normal MII interface                      | 20  |

|   |    | 2.3  | .2     | The RMII interface                            | 27  |

| 3 |    | Ted  | chnic  | cal aspects of implementation                 | 30  |

|   | 3. | 1    | Sig    | nal Integrity                                 | 30  |

|   |    | 3.1  | .1     | Introduction to Transmission Lines            | 32  |

|   |    | 3.1  | .2     | Modeling transmission lines                   | 33  |

|   |    | 3.1  | .3     | Termination of transmission lines             | 38  |

|   |    | 3.1  | .4     | The influence of Vias                         | 45  |

|   | 3. | 2    | Lay    | out and Timing                                | 48  |

|   |    | 3.2  | .1     | Calculation of timing requirements            | 48  |

|   |    | 3.2  | .2     | Layouting traces on the PCB                   | 49  |

|   |    | 3.2  | .3     | Layer stack, VCC and GND planes in the layout | 52  |

|   |    | 3.2  | .4     | Where to put the termination resistors        | 55  |

|   |    | 3.2  | .5     | Miscellaneous                                 | 55  |

|   | 3. | 3    | Sor    | ne words about the magnetics                  | 56  |

|   |    | 3.3  | .1     | Inductance in a transformer                   | 56  |

|   |    | 3.3  | .2     | Modeling a real world transformer             | 60  |

|   | 3. | 4    | Mea    | asuring and Measurement Equipment             | 62  |

|   |    | 3.4  | .1     | Measurement equipment                         | 62  |

|   |    | 3.4  | .2     | Some words about jitter                       | 64  |

| 4 |    | Lite | eratu  | re                                            | 71  |

| 5 |    | List | t of f | igures                                        | 72  |

6

#### Introduction 1

The provided information shall support the designer when developing products with DAVICOM's Ethernet products. Although we can offer additional assistance to our customers in the design-in phase we cannot guarantee the performance of the finished design nor can we assume responsibility for the operation, in production.

Nowadays, in embedded systems, there is a strong urge to be able to control these systems via a network-connection by means of a browser or similar tools. Therefore a lot of modern microcontrollers come with an integrated Ethernet MAC or can easily be attached to an external MACPHY.

As external PHY or MACPHY a variety of components is on the market. Davicom with its PHYs and MACPHYs, is one of the market leaders. Although Davicom offers other Ethernet products like switches, USB-to-Ethernet converters and Copper-to-Fiber converters, this paper mainly deals with their PHYs and MACPHYs and concentrates on the physical layer and Media Independent interfaces.

While digital logic gets faster and faster, digital design has to deal with higher frequencies and that is where they become "analog" again. Having signal rise times of 1ns or even below implies that you have to deal with frequencies up to the GHz range if we can believe M. Fourier and his theorem. PCB design for circuits like that, means that you have to obey a lot of rules concerning high frequency design and compliance with the EMI regulations.

Also a deeper knowledge of the safety regulations for telecommunication equipment is mandatory as well as a good understanding of the Ethernet standards - mainly the IEEE 802.3. Also you should think about implementing testability in an early stage of the design phase. Test equipment for compliance testing of the physical layer and for the media access layer (layer 1 and 2 of the OSI model) has become less expensive.

Last but not least there are software decisions, like using an operating system on the MCU or preferring to use a bare-metal-system. In the latter case you are responsible for all the drivers yourself which can make your software engineer's life very miserable. To ease his pain check for off-the-shelf drivers for the processor of your choice. If you decided to go with an operating system that already implements the lower layers you carefully should estimate the performance.

But now let's start with the first chapter ...

#### A look at the physical layer 2

#### 2.1 **Overview**

Since this is only a short paper we will only concentrate on 10Mbit and 100Mbit transfer rate and a copper medium. In particular this is a twisted pair medium (10BASE-T) and (100BASE-TX) can be found in IEEE802.3 (2008).

For Fast Ethernet (100BASE-TX) in addition the Medium Dependent part (TP-PMD) is described in ANSI INCITS 263-1995 (S2010) with changes described in IEEE802.3 clause 25.3 and 25.4. All IEEE802.x standards are available for download on the IEEE homepage. ANSI standards can be ordered as PDF for the ANSI organisation's webstore (http://standards.ieee.org/about/get/ and http://webstore.ansi.org/).

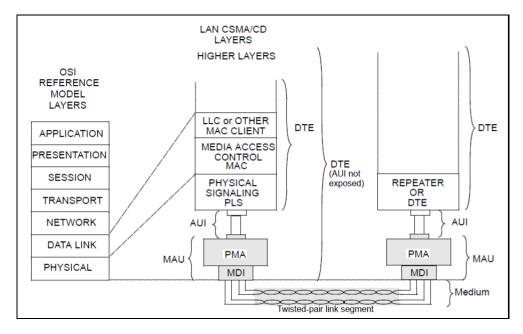

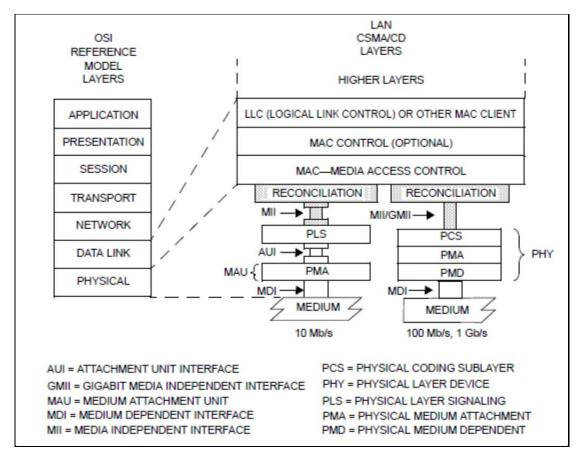

In order to understand the physical layer for 10BASE-T have a look at clause 14.1.1 of IEEE802.3. It shows the relationship between the OSI reference model and the IEEE 802.3 CSMA/CD LAN model:

Figure 1: 10BASE-T relationship to the OSI reference model (taken from IEEE 802.3-2008)

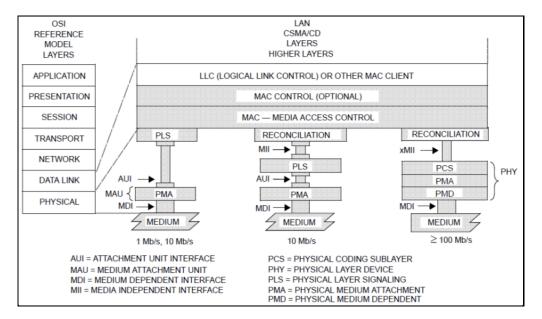

The physical twisted pair connection (medium) attaches to the Media Dependent Interface (MDI) which is part of the Media Access Unit (MAU) and is connected to the Physical Medium Attachment (PMA). This connects through the Attachment Unit Interface (AUI) to the Physical Layer Signaling (PLS). All together form the physical layer (layer 1) of the OSI model. This layer now attaches to layer 2 (the Data Link layer) via an Media Independent Interface (MII, not shown here). The last sublayer in OSI layer 1 is the Reconcilation Sublayer (RS) followed by the Media Access Control (MAC), the first sublayer of OSI layer 2. This is visible in the more general illustration in Figure 2.

Figure 2: More general relationship to the OSI reference model (taken from IEEE 803.3-

Generally what we call the "PHY" is a realization of the OSI physical layer with two interfaces: The Media Dependent Interface (MDI) and the Media Independent Interface (MII) which connects to the MAC of the processor. If the processor has no MAC we can use a MACPHY (a combination of the physical layer and parts of the data link layer (the driver that is realized on the processor also belongs to layer 2).

#### 2.2 The Media Dependent Interface

# 2.2.1 Physical connection

The MDI uses the RJ45 connection made of an Modular 8/8 receptacle and an Modular 8/8 plug with a standardized pinning

| Contact | MDI signal           |

|---------|----------------------|

| 1       | TD+                  |

| 2       | TD-                  |

| 3       | RD+                  |

| 4       | Not used by 10BASE-T |

| 5       | Not used by 10BASE-T |

| 6       | RD-                  |

| 7       | Not used by 10BASE-T |

| 8       | Not used by 10BASE-T |

Table 1: MDI connector for twisted pair link as shown in IEEE 803-3(2008) clause 14.5.1

There is also an MDI-X interface described where the MAU does an internal crossover for transmit and receive differential pair (which can be as simple as routing TD to RD and vica versa at the connector which then shall be marked with an X). If the PHY automatically detects the receive and transmit pair and does the crossover accordingly, this is called Auto-MDI-X. Most modern PHYs come with an Auto-MDI-X feature which can be switched on and off by Software.

## 2.2.2 Electrical safety

Although the Ethernet signal levels itself are SELV all network interfaces have a safety requirement! The general safety (refer to IEEC 802.3-2005 clause 14.7.1) shall meet IEC60950. The Network Safety (refer to IEEC 802.3-2005 clause 14.7.2) requires preventing from electrical hazard when touching a device that is connected via a network cable. Hazards that can appear are either direct contact of the LAN cable to power lines or any none safely extra-low voltage (SELV) circuits, static charge buildup on LAN cables, high energy transients due to for instance lightning and voltage potential differences between connected devices (see IEEE 802.3-2005 clause 14.7.2 a)-d). Safety grounding for such equipment and the impact of using a doubly insulated ac power supplies must be carefully considered and in compliance with IEC60950. The MAU to MDI interface requires an electrical isolation which can withstand at least one of the following tests (see IEC802.3-2005 clause 14.3.1.1):

- 1500V rms at 50Hz to 60Hz for 60s (see IEC60950-1:2005, 5.2.2)

- 2250V dc for 60s (see IEC60950-1:2005, 5.2.2)

- A sequence of ten 2400V impulses of alternating polarity, applied at intervals of not less than 1s (1.2/50us pulse as described in IEC6095-1:2005 Annex N)

There shall be no insulation breakdown and the resistance after the test shall be at least 500V dc (see IEC 60950-1:2005).

Please be aware that other requirements may be possible: If the device is a medical device, it must comply with IEC60601-1. For automotive design or aviation equipment there are other or additional requirements to meet which can depend on the customer as well.

The isolation requirement is the main reason why we need an Ethernet transformer and there should be no copper plane below the Ethernet magnetics and why this connection should be kept short (to meet a 1500V isolation requirement on a dense PCB which circuits are considered to be SELV is no fun!).

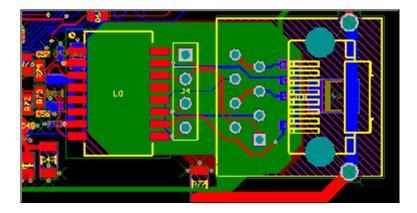

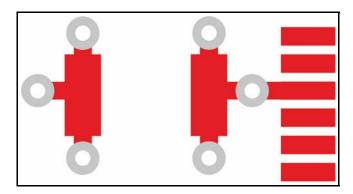

Figure 3: Layout example. The magnetics (L8) connect to the Modular receptacle.

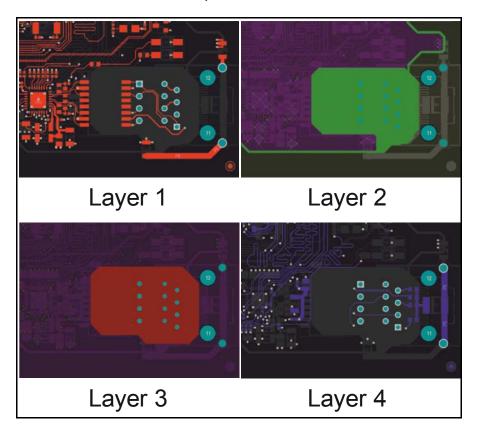

Figure 3 shows an example of a layout. J4 is there to connect to a piggy back PCB with an alternative connection and yes – it causes an additional impedance "bump" and that's not nice! The PHY is connected to the magnetic's pads on the right side by means of a differential strip line. Since the connection is really short the connection is not that critical. This is a 4 layer PCB with a VCC and GND plane on layer 2 and 3. The green polygon is the cutout in the VCC and GND plane. The sole reason for the cutout is the isolation requirement! Since without the plane an impedance control of the connection between magnetics and connector is almost impossible and therefore this connection should be as short as possible.

Figure 4: A single layer view of the PCB in Figure 3

So what does all this mean for the PCB layout in particular?

- In order to comply with the standard carefully keep the creepage and clearance distance that is required to comply with IEC60950-1. The creepage distance on PCBs does depend on the selected pollution degree. Usually pollution degree is 2 "which applies where there is only non-conductive pollution that might temporarily become conductive due to occasional condensation". Pollution degree 1 "applies where there is no pollution or only dry, nonconductive pollution". This means hermetically sealing of the PCB or conformal coating (solder resist is not conformal!). Creepage distance depends on the working voltage which is determined as described in IEC60950-1:2005 clause 2.10.2. The creepage usually is no problem in Ethernet networks since its RMS working voltage is in the SELV range. However the clearance and the transformer insulation are - since it depends on the peak working voltage and the maximum peak voltage of the transients. Determining the clearance can be done from Annex G of EN60950. Care must be taken when using an unearthed d.c. mains supply. If it's in the same building the transient voltage on the d.c. supply line is assumed to be 71V peak, if it's within the EUT "it shall be in accordance with 2.6.1 e)" (EN60950-1:2005 annex G.2.2) which means that if circuits – in case of a single failure – rely on a connection to Protective Earth in order to reduce transients must be reliable connected to PE. From the 1500V requirement as explained above (which assumes the Ethernet connection to be a TNV-1 or TNV-3 circuit (see IEC60950-1:2005, clause 2.3 and annex G 3). In accordance to table G.2 in annex G.6 for equipment that is used below 2000m above sea level the minimum clearance (reinforced insulation) is 1.6mm for all pollution degrees. Please read annex G.6 carefully because there are exceptions.

- Isolation of the transformer must also withstand 1500V RMS for a t least 60s. And this is also true on PCBs for the isolation to a GND plane. This is regulated in 2.10.6.4 of IEC60950-1:2005. So the best is to cut out all copper planes below the transformer and the connector.

- Special care must be taken on the dielectric strength of the capacitor from the Bob Smith Termination (we will discuss that later) to chassis which shall be 2KV.

To ease your pain you can use a connector with integrated magnetics and integrated termination. Those are available from a variety of vendors.

# 2.2.3 Electromagnetic Interference

Compliance with EMI regulations is always an issue with high speed interfaces and neglecting the basics of a high speed PCB design is a guaranty to fail. Before you go to the EMC lab for testing you have to determine if you device is an industrial (Class A) or residential, commercial or light industrial device (Class B). For Class A devices the emission requirement is lower but the immunity requirement is higher and vice

versa for Class B devices. I normally recommend to test the heavier requirement for both, Class A and Class B so that the device meats both criteria.

For radiated and conducted emission it is essential that no common mode signal can run over the Ethernet cable and use it as a resonant antenna (standing wave on the cable). This is directly related to the quality of the magnetics. They should have a common mode choke on the line side and a good common mode balance is also mandatory. The common mode choke cannot be on the PHY side since most PHYs can only sink current and therefore need a center tap to feed the transformer with a positive voltage. Any imbalance here causes common mode current to travel over the cable causing radiation. Also the quality of the cable has an impact. The Bob Smith termination of the cable reduces the common mode radiation. Although not being optimal it is widely used. "Bob Smith described in his patent (U.S. Patent, 5,321,372 issued 6/14/94) a method to reduce the longitudinal or common mode current on multipair conductor systems where the pairs are interrelated in a uniform manner. He alludes to the fact that the pair to pair relationships of a CAT5 cable form transmission lines in themselves [12]. As Jim points out in his Engineer's Notes Bob Smith seemed to calculate an impedance of about 145 ohms which hey says is wrong. As a result terminating the cable with about 52.3 ohms instead of Bob Smith's 75 ohms can improve the return loss significantly.

Since radiation can also be caused by the rest of the circuit and then coupling into the cable in the near field care should also be taken on a correct PCB layout (see Chapter xx about Signal Integrity). Of course radiation is also influenced by the shielding of the cable and the enclosure. Shielding can be considered a elongating the enclosure over the cable. If any modulated current flows over the shield (if one is used) it acts as an antenna itself. This can happen due to potential differences on each end of the cable. Proper low impedance attachment of the shield to earth is important.

# 2.2.4 10Base-T and 100Base-TX in particular

## 2.2.4.1 10Base-T

10Base-T is the Ethernet standard for transmission of 10 Mbit over an unshielded twisted pair cable which can have a length of max. 100m. Transmitter and receiver hereby are using different pairs. Only a point-to-point connection is possible (e.g. a maximum of two MAUs can be connected per segment. Due to the CSMA/CD the signal travelling time is limited and therefore the maximum length of a network is limited to 2500m. CSMA/CD means Carrier Sense Multiple Access which means that a station tests if there is no other signal at the link before it starts sending and Collision Detection which means that since CSMA is not enough to prevent a collision the collision is detected and the station then waits a random time before it tries to send again.

It is obvious that in a network that does not connect multiple links by means of a hub a full duplex operation is possible without any collision and therefore the CSMA/CD mechanism is not necessary (see also IEEE 802.3-2008, 1.1).

The electrical specification of the signal is as follows (see 802.3-2008, 14.3):

- The transmitter shall meet all requirements when connected to a load of 100 ohms

- For measurement a model for the twisted pair cable is used as described in Fig. 14-7 of IEEE 802.3-2008

- The peak differential voltage of the transmitter shall be between 2.2V and 2.8V when terminated with 100 ohms

- The transmitter shall provide equalization so that the output waveform falls within the template shown below for all transmitted data sequences (this means the eye diagram). Therefore the twisted pair model is used and the transmitter is connected through a balun. The transmitter is driven by a pseudo random Manchester code sequence with a minimum repetition period of 511 bits

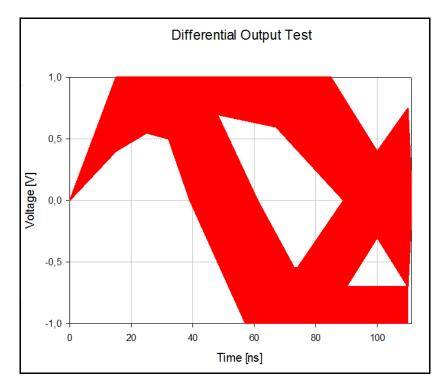

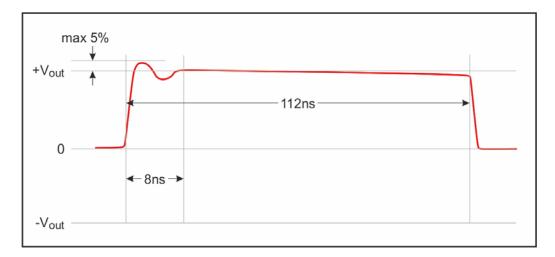

Figure 5: Mask for differential output test for a 10Base-T signal

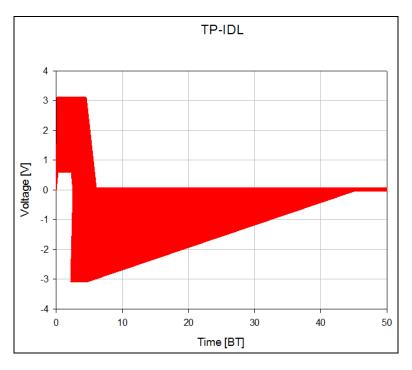

• When no data is sent the MAU sends and idle signal (see waveform below) followed by an repeated 16ms +/-8ms period of silence and a link test pulse

Figure 6: Idle Pulse Mask for a 10Base-T signal

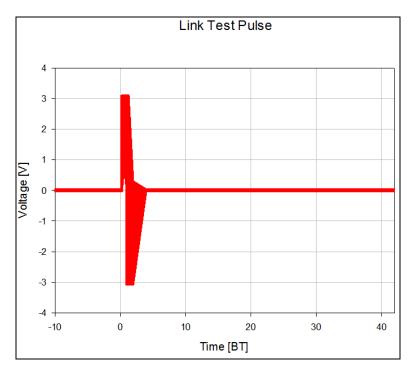

Before the link is established the MAU only sends link test pulses (see waveform below). The receiving MAU monitors the receive line either for idle and link test pulses or incoming data. If none is received for a time between 50ms and 150ms the MAU enter the Link Test Fail state which is left when a number of link test pulses (between 2 and 10) are received.

Figure 7: Link Test Pulse Mask

It is strongly recommended that Autonegotiation is used to determine either half or full duplex mode and the bit rate (10Base-T or 100Base-T).

Since the receiver needs to synchronize to the clock of the transmitter and there is no separated clock line the clock needs to be recovered by means of a PLL from the data. To accomplish that a special coding is used to guarantee either synchronizing of the receiver PLL and keep it locked while a packet is received:

The MAU uses Manchester Coding to send the data. This means that the signal will change its state in the middle of a data bit. A falling edge defines a logical 1 and a rising edge define a logical 0 (the originally defined Manchester Code does it vise versa). Using Manchester coding also provides us with a DC bias free line signal. The disadvantage of the Manchester Coding is that the bandwidth is doubled.

For synchronization an Ethernet packet (Ethernet frame) as defined on the Logical Link Layer (Layer2, the MAC layer) starts with a 7 byte preamble of hex AA followed by a start of frame delimiter (one byte, hex AB). Then the rest of the frame follows.

## 2.2.4.2 100Base-TX

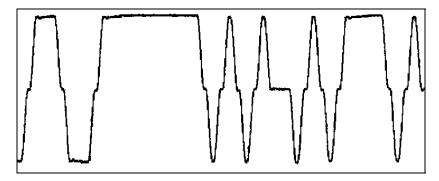

100Base-T or Fast Ethernet comes with a family of 100Mb/s physical layers which either uses an electrical or optical interface allowing only two participants per segment. We only discuss the 100Base-TX interface (electrical, dual twisted pair). The physical layer relates to ANSI INCITS 263-1995 (S2010) standard for Fiber Distributed Data Interface (FDDI) and Token Ring Twisted Pair Physical Layer Medium Dependent (TP-PMD). The coding of 100Base-TX is completely different from the coding used for 10Base-T: The MDI uses MLT3 coding on the line which means that a1 is encoded as a change of level and a 0 is encoded as no change. MLT3 uses three levels of logic (ternary signal), named (+,0,-). Since in a sequence of logic 1's the level changes are in the fixed order (0, +, 0, -) the bandwidth of the signal is only 1/4 of the NRZ input before encoding. The Problem is that for a sequence of 0's there is no level change and therefore a clock recovery is not possible. To overcome this the original input on a byte level is separated in two 4bit nibbles and each nibble passes a 4B5B-Encoder which ensures that there is no sequence of five 1's or five 0's. In addition now also special signal (called k-characters) are available which can be used for synchronization and signaling. The 4V5B-Coding increases the NRZ-Bitrate of 100Mb/s to 124Mb/s. Therefore the maximum bandwidth is 125MHz x  $\frac{1}{4}$  = 31.25MHz.

Figure 8: Typical MLT-3 Signal

According to ANSI INCITS 263-1995 there are requirements regarding that signal which can be summarized as follows:

| Characteristics                       | Minimum | Maximum | Units |

|---------------------------------------|---------|---------|-------|

| Differential Signal, UTP, zero-peak   | 950     | 1050    | mVpk  |

| Differential Signal, STP, zero-peak   | 1165    | 1285    | mVpk  |

| Signal Amplitude Symmetry (pos./neg.) | 98      | 102     | %     |

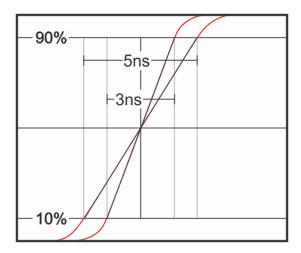

| Rise and Fall Time                    | 3.0     | 5.0     | ns    |

| Rise and Fall Time Symmetry           | 0       | 0.5     | ns    |

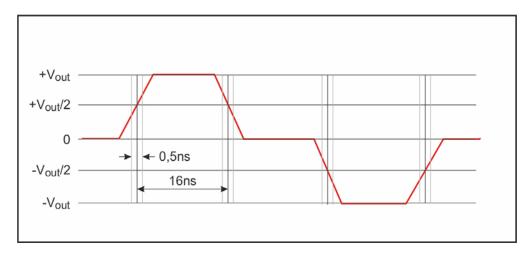

| Duty Cycle Distortion, peak-to-peak   | 0       | 0.5     | ns    |

| Transmit Jitter (HLS)                 | 0       | 1.4     | ns    |

| Overshoot                             | 0       | 5       | %     |

**Table 2: Twisted Pair Output Interface characteristics**

The requirement for the waveform overshoot also requires that "any overshoot or undershoot transient shall have decayed to within 1% of the steady state voltage within 8ns following the beginning of the differential signal transition".

**Figure 9: Active Output Interface Overshoot**

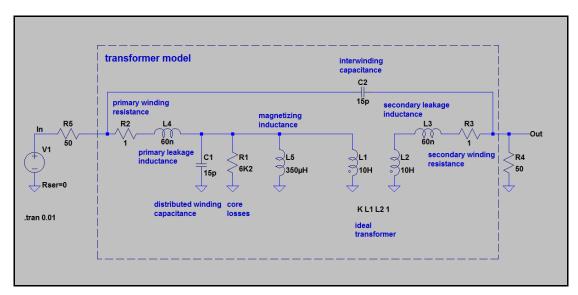

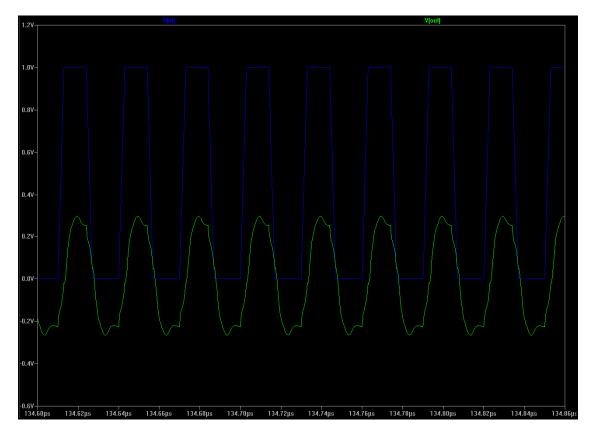

Also the signal droop is limited. Since Baseline Wander Tracking of the receiver depends on the droop the worst case droop is limited. The droop is directly related to the transformers open circuit inductance (OCL). ANSI INCITS 263-1995 therefor requires a minimum worst case OCL of 350µH with any DC bias current between 0mA and +8mA.

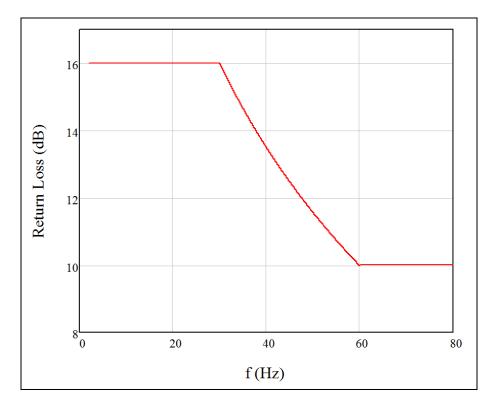

Table 2 does not show the Return Loss requirement. The Interface shall meet the Return Loss requirements below for any specified line impedance:

- Greater than 16dB from 2MHz to 30MHz

- Greater than (16 20 log (f / 30MHz))dB from 30MHz to 60MHz

- Greater than 10dB from 60MHz to 80MHz

**Figure 10: Return Loss of Active Output Signal**

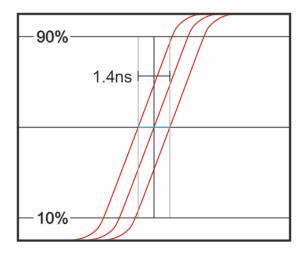

The Rise/Fall times are defined as the time from 10% of the signal amplitude to 90% of the signal amplitude.

Figure 11: Minimum and maximum rise time

The maximum duty cycle distortion is defined as the maximum deviation from a time difference of 16ns between the 50% amplitude values of the signal when fitted to a 16ns time grid.

**Figure 12: Duty Cycle Distortion**

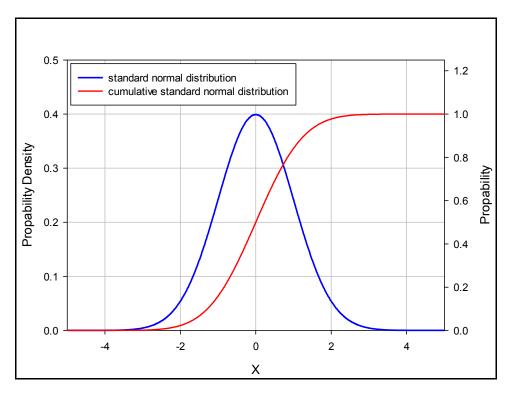

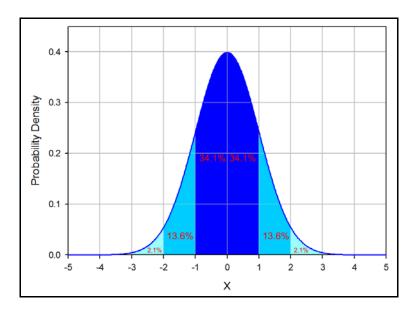

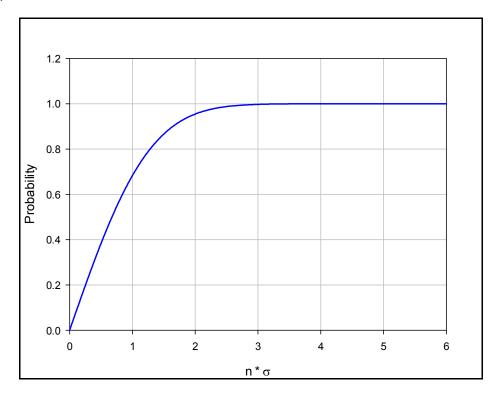

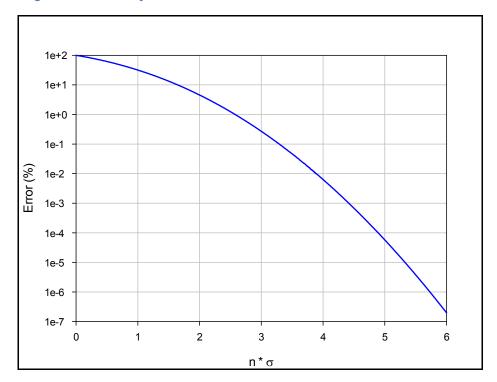

The maximum jitter requirement means peak to peak jitter  $(6\sigma)$ .

Figure 13: Maximum Peak-toPeak Jitter

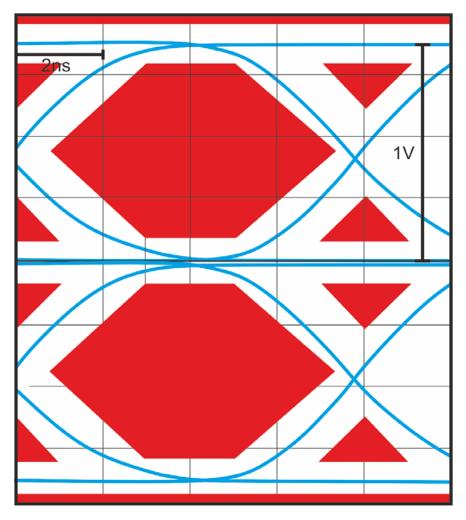

Summarizing all requirements, a simple eye pattern mask test can be defined. Though it is not mandatory it easily lets you qualify a 100Base-TX signal. A lot of common oscilloscopes nowadays are capable of performing the tests as described above using a differential active probe and a special software.

Figure 14: Mask definition for Eye Pattern Test (see Annex J of ANSI INCITS 263-1995

Since it should be possible to connect a legacy 10Base-T device to 100Base-TX segments it is strongly recommended that the PHY is capable of recognizing whether a 10Base-T or 100Base-TX device is connected to it and switch to the correct physical layer. This mechanism is called autonegotiation. In 100Base-TX segments the normal link pulse (NLP) is replaced by a fast link pulse (FLP). It is also transmitted every 16ms (+/-8ms) as the 10Base-T NLP. The 10Base-T PHY recognizes a NLP when receiving an FLP and therefore they assume a link but they are not capable of recognizing the information coded in the FLP. Each FLP has a duration of 100ns (as well as the NLP pulse) but the single NLP pulse is replaced by a burst of a maximum of 97 evenly spaced 100ns pulses. The pulse to pulse time is typ. 62.5µs. The odd pulses are the clock pulses and the even pulses are the data pulses. Omitting a data pulse means a logical 0 while a logical one means that the data pulse is present. For a detailed description see IEEE 803.3-2008, clause 28.

ETH-Brevier.docx

#### The Media Independent Interface 2.3

## 2.3.1 The normal MII interface

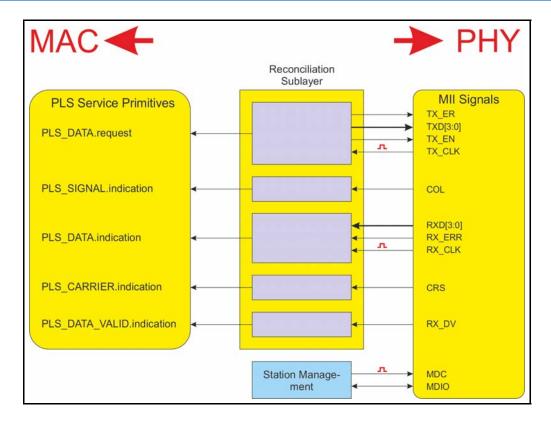

Having discussed the media dependent interfaces physics we now have a closer look at the media independent interface which connects the PHY to the MAC. The relationship to the OSI reference model is shown in IEEE 803.3-2008, clause 22.1.

Figure 15: MII relationship to the ISO/IEC Open System Interconnection (OSI) reference model and the IEEE 802.3 CSMA/CD LAN model (from IEEE 803.3-2008)

The Reconciliation Sublayer is the logical part of the interface between the MAC and the PLS and the MII is the physical part. Although the MII interface is capable of driving a shielded cable it normally resides directly on the PCB.

The signals use TTL signal levels and therefore are interoperable with 3.3V and 5V logic (please verify if a 3.3V device does really tolerate 5V inputs. As an example the DAVICOM DM9161C does).

The MII interface is a synchronous interface with a clock frequency of nominally 25MHz. The interface uses 4 data lines to transmit and receive data. The PHY sources the clock for the transmit and receive part of the interface.

The following figure gives an overview of the signals of the MII interface and the mapping between MII signals and PLS service primitives.

Figure 16: Reconciliation Sublayer (RS) inputs and outputs and STA connection to MII (from IEEE 803.3-2008)

In order to implement the interface on a PCB or using a shielded cable it is crucial to meet all electrical requirements of the interface and have a look at the signal integrity. We will not discuss connecting multiple PHYs to a MAC although this is possible but only a point-to-point connection since in most applications only one PHY is attached.

Since the MII interface uses TTL thresholds the following applies:

| Signal                                                                         | Minimum | Maximum         |

|--------------------------------------------------------------------------------|---------|-----------------|

| Output logic high level ( $V_{OH}$ ), $I_{OH} = -4mA$                          | 2.4V    | $V_{cc}$        |

| Output logic low level $(V_{OL})$ ), $I_{OL} = 4mA$                            | 0V      | 0.4V            |

| Input logic high level (V <sub>IH</sub> )                                      | 2V      | V <sub>cc</sub> |

| Input logic low level (V <sub>IL</sub> )                                       | 0V      | 0.8V            |

| Input high current $I_{IH}$ ( $V_I = 5.25V$ ) (all except COL, MDC, MDIO)      | -       | 200μΑ           |

| Input high current $I_{IH}$ ( $V_I = 5.25V$ ) (COL, MDC, MDIO at input of PHY) | -       | 20μΑ            |

| Input high current $I_{IH}$ ( $V_I = 5.25V$ ) (MDIO at input of STA)           | -       | 3000μΑ          |

| Input low current $I_{IL}$ ( $V_I = 0V$ ) (all except COL, MDC, MDIO)          | -20µA   | -               |

| Input low current $I_{IL}$ ( $V_I = 0V$ ) (COL at input of RC sublayer)        | -200µA  | -               |

| Input low current $I_{IL}$ ( $V_I = 0V$ ) (MDC at input of PHY)                | -20µA   | -               |

| Input low current $I_{IL}$ ( $V_I = 0V$ ) (MDIO at input of STA)         | -180µA  | -      |

|--------------------------------------------------------------------------|---------|--------|

| Input low current $I_{IL}$ ( $V_I = 0V$ ) (MDIO at input of PHY)         | -3800µA | -      |

| Input quiescent current $I_{IQ}$ ( $V_I = 2.4V$ ) (MDIO at input of STA) | -       | 1450μΑ |

| Input quiescent current $I_{IQ}$ ( $V_I = 2.4V$ ) (MDIO at input of PHY) | -1450μA | -      |

Table 3: DC characteristics of MII signals

The input capacitance for all signals other than MDIO shall not exceed 8pF. For the MDIO signal the input capacitance shall not exceed 10pF.

If using a twisted pair cable for connection the single ended impedance shall be  $68\Omega$ +/-10% (using one conductor of the pair as the return conductor). The propagation delay of the cable shall not exceed 2.5ns.

However if you design the interface on a PCB will more have to deal with transmission lines with an impedance between  $50\Omega$  and  $60\Omega$ .

At least for the clock signals it is mandatory to avoid double triggering due to over/undershoot or superposition of the reflected wave. Although there is no hint for the needs of an external series resistor in DAVICOMs application circuits (IEE 802-3-2008 requests this if necessary) I recommend placing a series resistor for the clock lines to adapt the driver's output impedance to the impedance of the transmission line and determine the series resistor value by measurement ( $22\Omega$  is a good starting value for a 3.3V device; check also Annex 22B.1 of IEEE802-3-2008). If the resistor is not needed then populate  $0 \Omega$ .

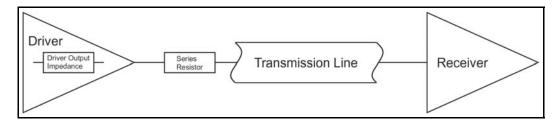

Figure 17: Typical PCB connection between driver and receiver.

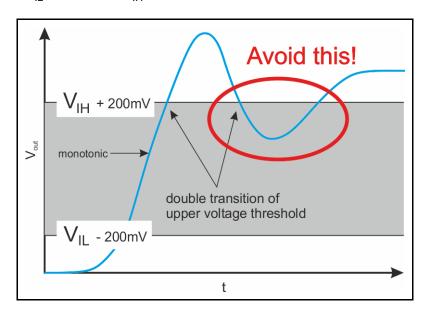

If insufficient series termination is used the reflected wave can cause double triggering if it passes through switching threshold of the receiver. IEEE802.3-2008 (Clause 22.4.3.2) states: "The initial incident potential change arriving at the receiving end of a point-to-point MII signal path plus its reflection from the receiving end of the path must switch the receiver input potential monotonically from a valid high (one) level to  $Vil \le Vil(max) - 200 \text{ mV}$ , or from a valid low (zero) level to  $Vih \ge Vih(min) + 200 \text{ mV}$ . Subsequent incident potential changes arriving at the receiving end of a point-topoint MII signal path plus their reflections from the receiving end of the path must not cause the receiver input potential to reenter the range Vil(max) – 200 mV < Vi <

Vih(min) + 200 mV except when switching from one valid logic level to the other. Such subsequent incident potential changes result from a mismatch between the characteristic impedance of the signal path and the driver output impedance."

#### This means that

- 1. The Receiver switches on the superposition of the incident wave and the reflected wave. Since the receiver has a high input impedance the reflection coefficient is 1. The strip line and the driver output resistance form a voltage divider and the incident wave has a potential of Vout/2. The reflected wave also has a potential of Vout/2 due to the reflection coefficient and superposition of both waves sum up to a potential of Vout.

- 2. Subsequent potential changes and reflections shall not enter the forbidden range of  $V_{IL}$ -200mV to  $V_{IH}$ +200mV.

Figure 18: Double switching caused by superposition of the reflected wave

Now let's have a closer look at the signals of the MII interface:

| Signal | Function                                                                                                                                                                                                                                                                                                                                                           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX-CLK | The continuous transmit clock is the timing reference for RX-DV, RXD[3.:0] and RX-ER. It is sourced by the PHY and has a nominal frequency of 25MHz (at 100Mbit/s) and 2.5MHz (at 10Mbit/s) (25% of the nominal transmission rate). The duty cycle is between 35% and 65% and the frequency deviation shall be no more than ±100ppm                                |

| RX-CLK | The continuous transmit clock is the timing reference for TX-EN, TXD[3.:0] and TX-ER. It is sourced by the PHY and has a nominal frequency of 25MHz (at 100Mbit/s) and 2.5MHz (at 10Mbit/s) (25% of the nominal transmission rate of 100Mbit/s). The duty cycle is between 35% and 65%. A guaranteed phase relationship between TX-CLK and RX-CLK is not required. |

| TX-EN  TXD[3:0]                        | Indicates that the RC sublayer is presenting valid nibbles (on TXD[3:0]). It is asserted synchronously with the first nibble of the preamble and remains asserted until all nibbles have been sent. Deassertion takes place prior to the first TX-CLK following the last nibble. TX-EN is an input of the PHY  These signal lines present the data nibbles on the MII interface.  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | They are an output of the PHY and transition synchronously with respect to TX-CLK. TXD[3:0] are only valid when TX-EN is asserted. TXD[0] is the least significant bit of the data nibble. TXD[3:0] are inputs of the PHY.                                                                                                                                                        |

| TX-ER                                  | TX-ER signals a transmit coding error and is an input of the PHY. It transitions synchronously with respect to TX-CLK. While TX-ERR and TX-EN is asserted the MAC transmits one or more symbols that are not part of the valid data. In 10Mbit/s mode the signal is ignored                                                                                                       |

| RX-DV                                  | RX-DV is an output of the PHY. It indicates that valid data is presented on RXD[3:0].                                                                                                                                                                                                                                                                                             |

| RX-ERR                                 | RX-ERR is an output of the PHY and signals a coding error to the RC layer (or any error that the PHY can detect). RX-ERR is only valid while RX-DV is asserted.                                                                                                                                                                                                                   |

| CRS                                    | CRS is the carrier sense signal and is an output of the PHY. It is asserted when either the transmit or receive medium is nonidle. It is deasserted when both the transmit and receive media are idle. CRS also remains asserted throughout the duration of a collision condition. CRS is not required to be synchronous to TX-CLK or RX-CLK.                                     |

| COL                                    | COL is an output of the PHY and signals a collision on the medium. It remains asserted while the collision persists. COL is not required to be synchronous to TX-CLK or RX-CLK.                                                                                                                                                                                                   |

| MDC                                    | MDC is sourced by the station management entity of the MAC and is an input of the PHY. It is the timing reference for the transfer of information on the MDIO signal. MDC is aperiodic and has no maximum high or low times. The minimum high and low times for the MDC signal are 160ns each and the minimum period is 400ns. DM9161C for instance allows a period of 80ns here. |

| MDIO                                   | MDIO is a bidirectional signal that is used to transfer control information and status between PHY and STA. It is driven and samples synchronously with respect to MDC                                                                                                                                                                                                            |

**Table 4: Signals of the MII interface**

Since we will concentrate on the physics of the interface we will not describe the protocol used on the MII interface here. Please refer to IEEE802.3-2008 clause 22.2.3 and 22.2.4.

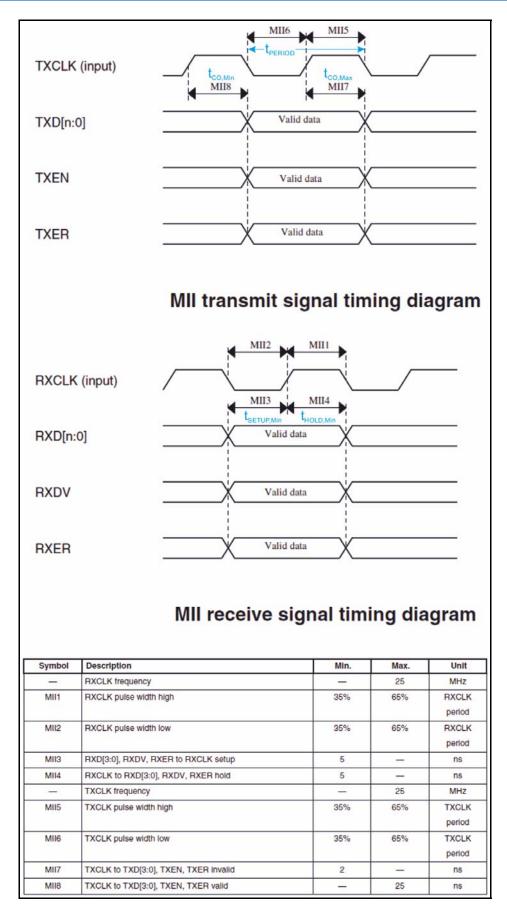

Let's have a look at the timing of the signals: All synchronous signals of the MII interface are related to a clock edge. Output signals have a clock-to-output delay from the clock edge they refer to until they are valid (t<sub>CO</sub>). All input signals need a minimum

setup time from the time they are valid until the clock edge they reference to (t<sub>SETUP</sub>) and a minimum hold time they must be valid after the clock edge (t<sub>HOLD</sub>).

Figure 19: Timing of synchronous signals

| Signal   | Clock To<br>Output   | Setup Time | Hold Time | Clock Edge    |

|----------|----------------------|------------|-----------|---------------|

| TXD[3:0] | Min 0ns<br>Max 25ns  |            |           | TX-CLK rising |

| TX-EN    | Min 0ns<br>Max 25ns  |            |           | TX-CLK rising |

| TX-ER    | Min 0ns<br>Max 25ns  |            |           | TX-CLK rising |

| RXD[3:0] |                      | Min 10ns   | Min 10ns  | RX-CLK rising |

| RX-DV    |                      | Min 10ns   | Min 10ns  | RX-CLK rising |

| RX-ER    |                      | Min 10ns   | Min 10ns  | RX-CLK rising |

| MDIO     | Min 0ns<br>Max 300ns | Min 10ns   | Min 10ns  | MDC rising    |

Table 5: Signal timing as specified in clause 22.3 of IEEE 802.3-2008

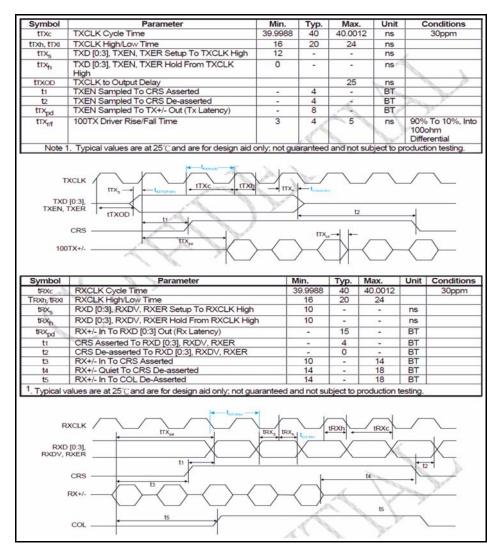

Since IEEE 802.3-2008 only specifies one side of the interface (e.g. for signals related to TX-CLK only the  $t_{\text{CO}}$  of the transmitter is defined and the  $t_{\text{SETUP}}$  and  $t_{\text{HOLD}}$  of the receiver is not you should check the timings of the PHY and the MAC from their datasheets carefully. In the following we will do that for one of Freescale's Kinetis processors and Davicom's DM9161C PHY.

Figure 20: MII switching characteristics of Freescale's MK60DN512ZVLQ10

The MII timing specification of the processor must be compared to the timing specification of the PHY.

Figure 21: MII-Timing of DM9161C

Please notify that for the RX-Timing of the PHY a setup and hold time is specified. Since RXD[3:0] for instance, is an output of the PHY the clock-to-output time is required and this is derived from those timings (see Figure 21).

## 2.3.2 The RMII interface

The RMII interface has been established by the RMII consortium. The actual release of the specification is from 1997 and can be downloaded from National Semiconductor's website (http://www.national.com/assets/en/other/rmii 1 2.pdf). The interface reduces the number of data lines and control lines but doubles the clock frequency.

Most of the tables and figures in the following paragraphs are taken from the RMII specification without explicit notification.

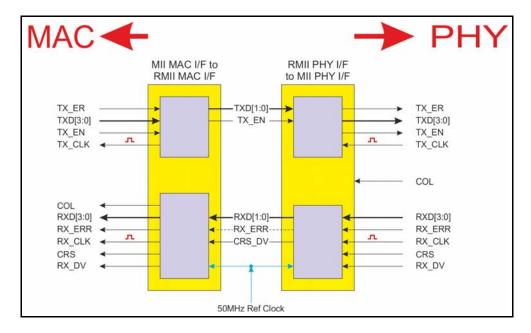

Figure 22: Signal Reconciliation Map of the RMII interface

The RMII signal definition is as follows:

| Signal Name | Direction<br>(with respect<br>to the PHY) | Direction<br>(with respect<br>to the MAC) | Use                                                                     |

|-------------|-------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------|

| REF_CLK     | Input                                     | Input or Out-<br>put                      | Synchronous clock reference for receive, transmit and control interface |

| CRS_DV      | Output                                    | Input                                     | Carrier Sense / Receive Data<br>Valid                                   |

| RXD[1:0]    | Output                                    | Input                                     | Receive Data                                                            |

| TX_EN       |                                           | Output                                    | Transmit Enable                                                         |

| TXD[1:0]    |                                           | Output                                    | Transmit Data                                                           |

| RX_ER       | Output                                    | Input (not required)                      | Receive Error                                                           |

**Table 6: RMII Specification Signals**

The reference clock is a continuous clock that is either sourced by the MAC or an external source (clock distribution device). The reference clock shall be 50MHz ±50ppm with a duty cycle between 35% and 65%. The PHY shall use the reference clock as the network clock.

CRS DV shall only be asserted by the PHY when the medium is nonidle. It is asserted asynchronously on detection of carrier. Loss of carrier shall result in a deassertion of CRS DV synchronous to the reference clock. RXD[1:0] is valid only when CRD DV is asserted.

RXD[1:0] and TXD[1:0] transition synchronously to the reference clock. They carry the di-bits of a package received by the PHY resp. a package that should be sent by the PHY.

ETH-Brevier.docx

TX\_EN is asserted synchronously with the first nibble of the preamble and remains asserted until all data of the packet is sent. It is negated prior to the first REF CLK rising edge that follows the final di-bit of a frame. It indicates that the transmit data is valid.

Please notice that the RMII interface – other than the MII interface – uses a single clock for receive and transmit path which can either be source by the MAC or an external clock distribution.

TTL signal levels are used. All inputs shall be able to tolerate input potentials up to 5.5V. All connections are intended to be point-to-point connections on a PCB. If the connections are short paths, transmission line reflections can be ignored. Characteristic impedance or a connector is outside the scope of the RMII specification. I recommend to use impedance controlled transmission lines anyway and to take special care of the clock signal (proper serial termination, we'll discuss this later).

| Parameter          | Symbol          | Conditions   | Min | Тур | Max | Units |

|--------------------|-----------------|--------------|-----|-----|-----|-------|

| Input High Voltage | $V_{IH}$        |              | 2.0 |     |     | V     |

| Input Low Voltage  | $V_{IL}$        |              |     |     | 8.0 | V     |

| Input High Current | I <sub>IH</sub> | $V_1 = 5.5V$ |     |     | 200 | μA    |

|                    | I <sub>IH</sub> | $V_1 = 3.6V$ |     |     | 200 | μΑ    |

| Input Low Current  | I <sub>IL</sub> | $V_1 = 0.0V$ | -20 |     |     | μΑ    |

**Table 7: RMII interface DC characteristics**

The AC parameters are specified in the following table.

| Parameter                                                                               | Symbol            | Min | Тур | Max | Units |

|-----------------------------------------------------------------------------------------|-------------------|-----|-----|-----|-------|

| REF_CLK Frequency                                                                       |                   |     | 50  |     | MHz   |

| REF_CLK Duty Cycle                                                                      |                   | 35  |     | 65  | %     |

| Data Setup Time to rising edge of REF_CLK for TYD[1:0], TX_EN, RXD[1:0], CRS_DV, RX_ER  | T <sub>SU</sub>   | 4   |     |     | ns    |

| Data Hold Time from rising edge of REF_CLK for TYD[1:0], TX_EN, RXD[1:0], CRS_DV, RX_ER | T <sub>HOLD</sub> | 2   |     |     | ns    |

**Table 8: RMII interface AC characteristic**

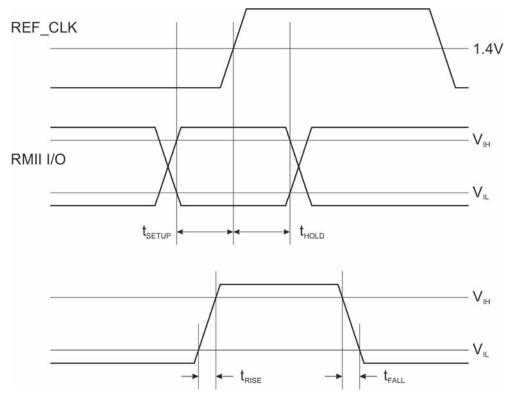

All output drivers shall be capable to drive into a minimum of 25pF while meeting all requirements. This allows about 12 inches of PCB trace. The timing measurement shall be referenced to the point where the reference clock crosses a reference level of 1.4V to the valid input or output at either  $V_{IL}$  or  $V_{IH}$  level. The rise and fall times shall be measured between  $V_{IL}$  and  $V_{IH}$  and shall be between 1ns and 5ns.

Figure 23: Switching waveforms of MII interface for AC Measurement

#### 3 **Technical aspects of implementation**

#### 3.1 **Signal Integrity**

Implementing an Ethernet interface also means taking special care of signal integrity which means that for proper functionality and PCB design a knowledge about behavior of high speed signals is indispensable. Although the clock frequency of the signal may be quite low, the fast rise and fall times of those signals implies harmonics up into the GHz range. These harmonics can also cause radiation if they find an antenna. On a PCB, magnetic loop antennas can also occur if for instance you do not have a contiguous ground plane. For harmonics with a frequency of 1GHz the wavelength on FR4 is about 15cm and a  $\lambda$ /4 antenna would have a length of about 3.7cm which is in the range of a trace length on the PCB. Poor impedance matching can cause reflections which superimpose the signal and can cause false or double switching, especially of clock lines. An impedance controlled design with a contiguous ground plane therefore is highly recommended.

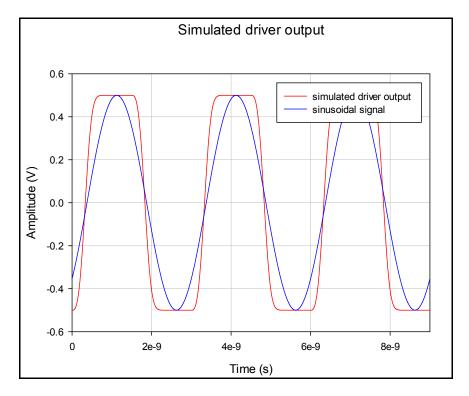

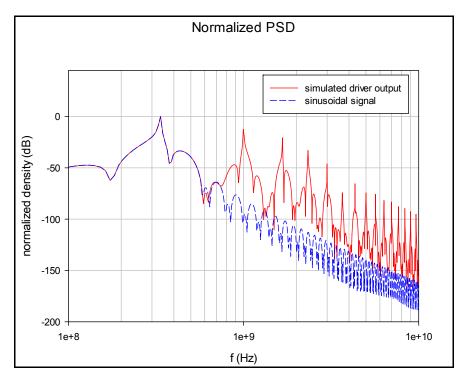

Figure 24: Simulation of a typical driver output and fitted sinusoidal signal

Figure 25: PSD of simulated driver output and sinusoidal signal

As you can clearly see from Figure 25 the more rectangular simulated driver output has harmonics up to 3GHz (-50dB) compared to the sine signal (Blackman-Harris Window used before FFT calculation). Those harmonics contribute to the EMI behavior of the device.

## 3.1.1 Introduction to Transmission Lines

RevisionOne GmbH Dr. Martin Moerz

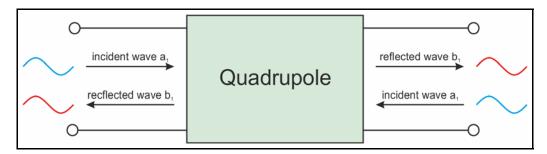

A transmission line is a special structure on a PCB (or a special cable) that is used for point-to-point wiring for high frequency circuits since they have less distortion, less radiation and less crosstalk than an ordinary PCB trace or wire. The transmission line guides a TEM wave from one point to another. As a rule of thumb a PCB trace (or cable) should be treated as transmission line if the wavelength of the conducted ac signal is higher than 10 times the length of the connection. A transmission line can be modeled as a two-port network or quadrupole. An incident wave is transported through the quadrupole while a part of the wave is reflected. This is true for both directions. The amount of conducted and reflected power can be described by means of the Scattering Parameters (S-Parameters).

Figure 26: Quadrupole with incident an reflected waves at it's ports

The scattering parameters and the input and output in terms of square root of power form the following matrix equation:

$$\begin{bmatrix} b_1 \\ b_2 \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix} \begin{bmatrix} a_1 \\ a_1 \end{bmatrix}$$

(3.1-1)

Expanding the matrix yields:

$$b_1 = S_{11}a_1 + S_{12}a_2$$

$$b_2 = S_{21}a_1 + S_{22}a_2$$

(3.1-2)

(3.1-3)

$$b_2 = S_{21}a_1 + S_{22}a_2 \tag{3.1-3}$$

$S_{11}$  and  $S_{22}$  count for the reflection while  $S_{12}$  and  $S_{21}$  count for the transmission.

- S<sub>11</sub> is the input port voltage reflection coefficient

- S<sub>22</sub> is the output port voltage reflection coefficient

- S<sub>21</sub> is the forward voltage gain

- S<sub>12</sub> is the reverse voltage gain

The voltage relation results from the convention to write the input and output as square root of the power (see above).

Reflection is caused by impedance mismatch at the input or output of the quadrupole since the transmission line has a characteristic impedance Z<sub>0</sub> where Z<sub>0</sub> is (from Wikipedia: Wave impedance: <a href="http://en.wikipedia.org/wiki/Wave\_impedance">http://en.wikipedia.org/wiki/Wave\_impedance</a>)

$$Z_0 = \frac{E_0^-(x)}{H_0^-(x)} \tag{3.1-4}$$

which describes Z<sub>0</sub> as quotient of the electric and the magnetic field (in phasor representation). Taking the propagation medium into account this yields

$$Z_0 = \sqrt{\frac{j\omega\mu}{\sigma + j\omega\varepsilon}} \tag{3.1-5}$$

If the medium is a dielectric (the conductivity is 0) this can be simplified to

$$Z_0 = \sqrt{\frac{\mu}{\varepsilon}} \tag{3.1-6}$$

The characteristic impedance of free space calculates to

$$Z_0 = \sqrt{\frac{\mu_0}{\varepsilon_0}} = \sqrt{\frac{4\pi \cdot 10^{-7} \frac{H}{m}}{8.854 \cdot 10^{-12} \frac{F}{m}}} \approx 377\Omega$$

(3.1-7)

For a perfect dielectric medium the characteristic impedance is given by

$$Z_0 = \sqrt{\frac{\mu_0}{\varepsilon_0 \varepsilon_r}} \approx \frac{377}{\sqrt{\varepsilon_r}} \Omega \tag{3.1-8}$$

# 3.1.2 Modeling transmission lines

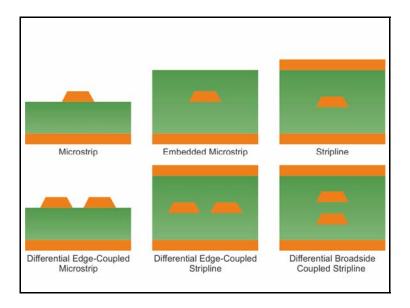

Calculating transmission line impedance on a PCB is not an easy thing. It means solving Maxwell's equations for this particular structure. There are several approximations that exist but I recommend to use a 2D- or 3D-FieldSolver like Polar Instrument's Si8000m (http://www.polarinstruments.com/). It is more precise than any approximation especially for differential striplines or microstrips.

Figure 27: Types of Microstrips and Striplines

Figure 27 shows the common types of transmission lines on PCBs. A trace that refers to one ground plane is called a Microstrip or Embedded Microstrip if embedded in the dielectric. A trace that is encapsulated between two ground planes is called a strip line. A differential signal can be transported with an Edge-Coupled Differential Microstrip (can also be embedded), an Edge-Coupled Differential Stripline or a Broadside Coupled Differential Stripline.

Now what is so different with transmission lines? First the voltage and the current on a transmission line if a function of both time and position.

$$V = f(s,t)$$

(3.1-9)

$I = f(s,t)$  (3.1-10)

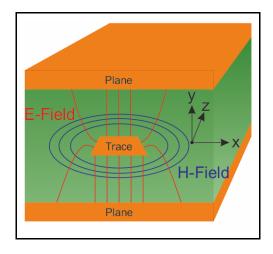

The voltage is related to the electric field while the current is related to the magnetic field.

Figure 28: Stripline with electric and magnetic field lines

E-Field and H-Filed form a transverse electromagnetic wave (TEM wave). E-Field and H-Field are directed transvers to the direction of propagation (the z-axis). Such waves propagate along structures composed of pairs of conductors. Since those fields have no divergence Ampère's law and Faraday's law fully describe a TEM field.

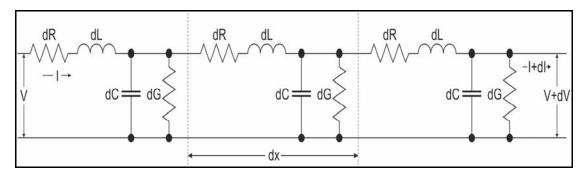

Striplines can be modeled as distributed element model.

Figure 29: Distributed model of a stripline

This means that the (in this case one-dimensional) transmission line is modeled as a linear concatenation of lumped circuit elements where each element represents an infinitesimal piece of the transmission line. The model parameters are:

| Model parameter | Comment                 | Unit |

|-----------------|-------------------------|------|

| dR              | Resistivity             | Ω/m  |

| dL              | Distributed Inductance  | L/m  |

| dC              | Distributed Capacitance | C/m  |

| dG              | Conductivity            | S/m  |

Table 9: Parameters of a lumped element of the transmission line's distributed model

The equation describing the above model can be derived from Maxwell's equation and is called Telegrapher's Equation.

$$\frac{\delta V(x)}{\delta x} = -(dR + j\omega dL)I(x)$$

(3.1-11)

$$\frac{\delta V(x)}{\delta x} = -(dR + j\omega dL)I(x)$$

$$\frac{\delta I(x)}{\delta x} = -(dG + j\omega dC)V(x)$$

(3.1-12)

Differentiating both equations yields:

$$\frac{\delta^2 V(x)}{\delta x^2} = \gamma^2 V(x)$$

$$\frac{\delta^2 I(x)}{\delta x^2} = \gamma^2 I(x)$$

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(3.1-14)

(3.1-15)

$$\frac{\delta^2 I(x)}{\delta x^2} = \gamma^2 I(x) \tag{3.1-14}$$

$$\gamma = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(3.1-15)

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(3.1-16)

Where  $\gamma$  is the transmission line's complex propagation constant and  $Z_0$  is the characteristic impedance. A solution of the above equations is:

$$V(x) = V_f e^{\gamma x} + V_r e^{-\gamma x} \tag{3.1-17}$$

$$I(x) = I_f e^{\gamma x} - I_r e^{-\gamma x}$$

(3.1-18)

Where x is the displacement from the load (negative towards source) and V<sub>f</sub>, V<sub>r</sub>, I<sub>f</sub>, I<sub>r</sub> are forward and reflected voltages and currents referring to the load (source: http://vk1od.net/transmissionline/TE/TE.htm). We now can rewrite the above equations:

$$V(x) = V_f(e^{\gamma x} + \Gamma e^{-\gamma x})$$

$$I(x) = I_f(e^{\gamma x} - \Gamma e^{-\gamma x})$$

(3.1-19)

(3.1-20)

$$I(x) = I_f(e^{\gamma x} - \Gamma e^{-\gamma x}) \tag{3.1-20}$$

Where  $\Gamma$  is the complex reflection coefficient at the load. With the load impedance Z<sub>load</sub> we yield:

$$\Gamma = \frac{Z_{load} - Z_0}{Z_{load} - Z_0}$$

$$\Gamma(x) = \Gamma \frac{e^{\gamma x}}{e^{-\gamma x}}$$

(3.1-21)

$$\Gamma(x) = \Gamma \frac{e^{\gamma x}}{e^{-\gamma x}} \tag{3.1-22}$$

We can now derive p and VSWR:

$$\rho = |\Gamma| \tag{3.1-23}$$

$$\rho = |\Gamma|$$

(3.1-23)

$$VSWR = \frac{1+\rho}{|1-\rho|}$$

(3.1-24)

For the quadrupole the input impedance for a transmission line of length I can now be calculated:

$$Z_{in} = Z_0 \frac{Z_{load} + Z_0 \tanh(\gamma l)}{Z_0 + Z_{load} \tanh(\gamma l)}$$

(3.1-25)

Also there is the following relationship between input voltage, input current, output voltage and output current:

$$V_{in} = V_{out} \cosh(\gamma l) + I_{out} Z_0 \sinh(\gamma l)$$

(3.1-26)

$$I_{in} = \frac{V_{out}}{Z_0} \cosh(\gamma l) + I_{out} \cosh(\gamma l)$$

(3.1-27)

For a complete derivation see[1].

We can now distinguish between a lossless transmission line where dR and dG equals zero and a lossy transmission line where dR and/or dG do not equal zero. For a lossless transmission line therefore the above equations can be simplified.

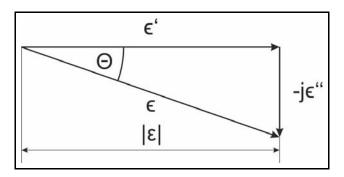

Since the permittivity of normal materials depends on the frequency of the electric field the permittivity is complex (a material's polarization does not respond instantaneously to an electric field change and therefore introduces a phase shift).

$$\varepsilon_r = \frac{\varepsilon'}{\varepsilon_0} - j \frac{\varepsilon''}{\varepsilon_0} \tag{3.1-28}$$

Where  $\varepsilon$  and  $\varepsilon$  are the real and imaginary part of the complex permittivity. It is obvious then that

$$\varepsilon_r = \varepsilon_r' - j\varepsilon_r'' \tag{3.1-29}$$

When talking about the  $\varepsilon_r$  of a PCB we mean the real part (the dielectric constant). The dielectric loss of a material can now be calculated from its complex permittivity (please remember that the parameters are a function of the frequency):

$$\tan \Theta = \frac{\varepsilon''}{\varepsilon'} \tag{3.1-30}$$

Where  $tan \Theta$  equals the dissipation factor.

Figure 30: Dissipations factor and complex permittivity as a vector diagram

For PCB materials the dissipation factor of FR4 is causing significant attenuation in the GHz range. For 100Mbit/s and 10Mbit/s FR4 can be used. For 1GBit and especially 10GBit Ethernet a suitable high frequency material should be selected. For higher frequencies also dG depends on the frequency due to the skin effect and dR depends on the frequency as well, due to the dielectric losses.

Since the propagation velocity of electric signals on PCBs can be estimated as

$$v_{prop} = \frac{c}{\sqrt{\varepsilon_r}} \tag{3.1-31}$$

The flight time of a signal on a PCB for a transmission line therefore can be calculated. Please be aware that vias and connectors add propagation delay as well.

### 3.1.3 Termination of transmission lines

Since source and load impedance and characteristic impedance of transmission lines interact, bad termination can lead to reflections [2]. For a driver injecting a signal into a transmission line a fraction of the signal is transported through the transmission line while another fraction is reflected. Since the transmitted fraction is a function of frequency we can introduce the input acceptance function  $A(\omega)$ :

$$A(\omega) = \frac{Z_0(\omega)}{Z_{source}(\omega) + Z_0(\omega)}$$

(3.1-32)

When propagating through the transmission line the signal becomes attenuated by the propagation function  $H(s,\omega)$ :

$$H(s,\omega) = e^{-s\sqrt{(R(\omega)+j\omega L)(j\omega C)}}$$

(3.1-33)

Remember that R depends on the frequency as well due to the skin effect. At the far end of the transmission line a fraction of the attenuated signal emerges. This fraction is also a function of the frequency and is called the output transmission function:

$$T(\omega) = \frac{2Z_{load}(\omega)}{Z_{load}(\omega) + Z_0(\omega)}$$

(3.1-34)

The fraction of the signal that is reflected back towards the source is called the farend reflection function:

$$R_2(\omega) = \frac{Z_{load}(\omega) - Z_0(\omega)}{Z_{load}(\omega) + Z_0(\omega)}$$

The signal now travels back towards the source, is attenuated by  $H(s,\omega)$  and reflects off the source impedance. The reflection function is the near-end reflection function:

$$R_1(\omega) = \frac{Z_{source}(\omega) - Z_0(\omega)}{Z_{source}(\omega) + Z_0(\omega)}$$

(3.1-35)

The first signal that emerges from the transmission line can now be calculated:

$$S_0(s,\omega) = A(\omega)H(s,\omega)T(\omega) \tag{3.1-36}$$

Successive emerging signals can be calculated:

$$S_N(s,\omega) = A(\omega)H(s,\omega)[R_2(\omega)H^2(s,\omega)R_1(\omega)]^N T(\omega)$$

(3.1-37)

The sum of all emerging signals can be calculated from:

$$S_{\infty}(s,\omega) = \sum_{n=0}^{\infty} S_n(s,\omega)$$

(3.1-38)

A closed-form equivalent exists:

$$S_{\infty}(s,\omega) = \frac{A(\omega)H(s,\omega)T(\omega)}{1 - R_2(\omega)H^2(s,\omega)R_1(\omega)}$$

(3.1-39)

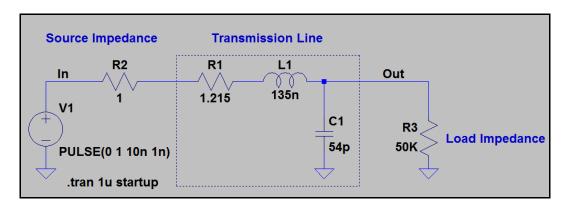

As an example we consider a stripline of 15in with a  $Z_0$  of  $50\Omega$  and propagation delay T<sub>P</sub> of 180ps/in. We calculate dL and dC:

$$dL = Z_0 T_P \tag{3.1-40}$$

$$dL = Z_0 T_P (3.1-40)$$

$$dC = \frac{T_P}{Z_0} (3.1-41)$$

We now model the stripline also as one lumped circuit and consider four cases for source impedance and load impedance.

Figure 31: Lumped model of the stripline with an excitation pulse (rise time 1ns) and a load

$$\begin{split} R &:= 0.081 \frac{\Omega}{\text{in}} \qquad Z_0 := 50\Omega \qquad 1 := 15 \text{in} \qquad T_p := 180 \frac{ps}{\text{in}} \\ L &:= Z_0 \cdot T_p \quad L = 9 \times 10^{-9} \frac{\text{H}}{\text{in}} \qquad C := \frac{T_p}{Z_0} \qquad C = 3.6 \times 10^{-12} \frac{\text{F}}{\text{in}} \\ A \Big( Z_{\text{source}}, \omega \Big) &:= \frac{Z_0}{Z_{\text{source}} + Z_0} \qquad H(s, \omega) := e^{-s \cdot \sqrt{(R + j \cdot \omega \cdot L) \cdot j \omega \cdot C}} \\ R_2 \Big( Z_{\text{load}}, \omega \Big) &:= \frac{Z_{\text{load}} - Z_0}{Z_{\text{load}} + Z_0} \qquad R_1 \Big( Z_{\text{source}}, \omega \Big) := \frac{Z_{\text{source}} - Z_0}{Z_{\text{source}} + Z_0} \\ T \Big( Z_{\text{load}}, \omega \Big) &:= \frac{2 \cdot Z_{\text{load}}}{Z_{\text{load}} + Z_0} \\ S_0 \Big( Z_{\text{source}}, Z_{\text{load}}, \omega, s \Big) &:= A \Big( Z_{\text{source}}, \omega \Big) \cdot H(s, \omega) \cdot T \Big( Z_{\text{load}}, \omega \Big) \\ f &:= 0 \text{Hz}, 1000000 \text{Hz} ... 1 \text{GHz} \end{split}$$

Figure 32: Stripline example

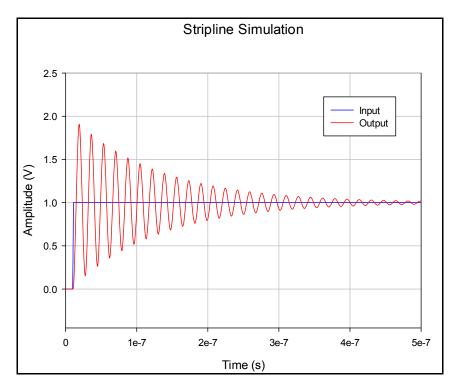

Case 1: Source impedance small and load impedance high.

$$Z_{source} = 5\Omega$$

$Z_{load} = 50K\Omega$

$A(100MHz) = 0.909$

$|H(15in, 100MHz)| = 0.988$

$arg(H(15in, 100MHz) = -15^{\circ}$

$T(100MHz) = 1.998$

$R_2(100MHz) = 0.998$

$R_1(100MHz) = -0.818$

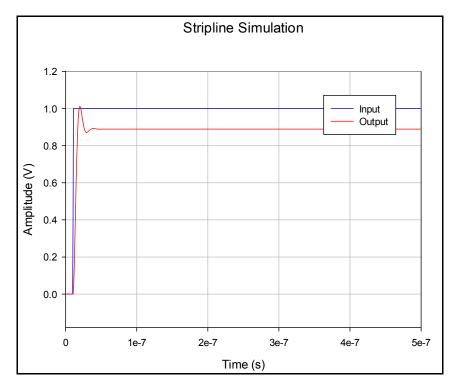

The amplitude at the load rises up to 1.8 times the input amplitude due to superposition of the incident and the reflected wave. The wave is reflected back and forth many times (excessive ringing).

Figure 33: SPICE Stripline Simulation of case 1

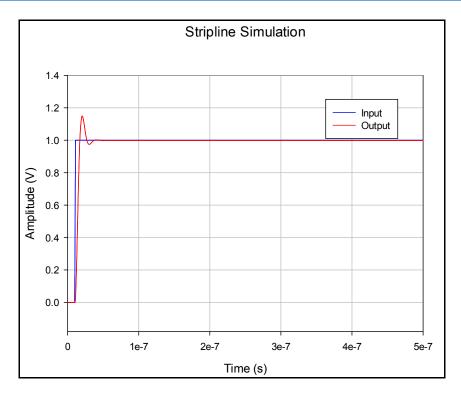

Case 2: Source impedance matched and load impedance high.

$$Z_{source} = 50\Omega$$

$Z_{load} = 50K\Omega$

$A(100MHz) = 0.5$

$|H(15in, 100MHz)| = 0.988$

$arg(H(15in, 100MHz) = -15^{\circ}$

$T(100MHz) = 1.998$

$R_2(100MHz) = 0.998$

$R_1(100MHz) = 0$

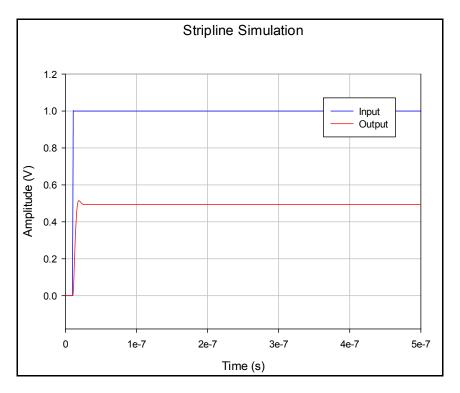

The amplitude at the load is round about the input amplitude due to superposition of the incident and the reflected wave where the transmission line and the source resistance for a voltage divider and therefore the incident wave is attenuated to 50% of the driver output voltage. The wave gets reflected and the reflection is absorbed in the source resistance; no further reflections occur.

Figure 34: SPICE Stripline Simulation of case 2

Case 3: Source impedance small and load impedance matched.

$$Z_{source} = 5\Omega$$

$Z_{load} = 50\Omega$

$A(100MHz) = 0.909$

$|H(15in, 100MHz)| = 0.988$

$arg(H(15in, 100MHz) = -15^{\circ}$

$T(100MHz) = 1$

$R_2(100MHz) = 0$

$R_1(100MHz) = -0.818$

The amplitude at the load is 90% of the input amplitude due to the voltage divider of the source impedance and the impedance of the stripline. Because the output is terminated, there is no reflection from the load side back to the source.

Figure 35: SPICE Stripline Simulation of case 3

Case 4: Source impedance matched and load impedance matched.

$$Z_{source} = 5\Omega$$

$Z_{load} = 50K\Omega$

$A(100MHz) = 0.5$

$|H(15in, 100MHz)| = 0.988$

$arg(H(15in, 100MHz) = -15^{\circ}$

$T(100MHz) = 1$

$R_2(100MHz) = 0$

$R_1(100MHz) = -0$

The amplitude at the load is about 50% of the input amplitude due to the voltage divider formed by the source impedance and the impedance of the transmission line. There is no reflection at all.

Figure 36: SPICE Stripline Simulation of case 3

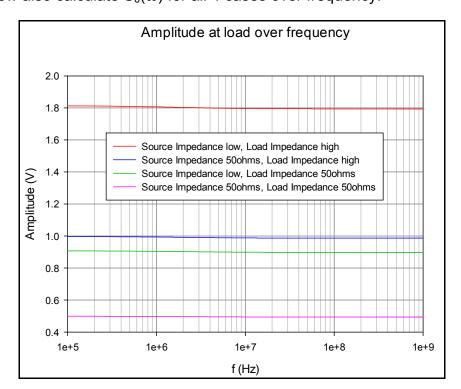

We can now also calculate  $S_0(\omega)$  for all 4 cases over frequency:

Figure 37:  $S_0(\omega)$  calculated for the above 4 impedance cases

If a transmission line is that short that  $H(s,\omega)$  is close to unity, we can simplify the equation for  $S_{\infty}(s,\omega)$  [2]:

$$S_{\infty}(s,\omega) = \frac{A(\omega)T(\omega)}{1 - R_2(\omega)R_1(\omega)}$$

(3.1-42)

$$S_{\infty}(s,\omega) = \frac{\frac{Z_0}{Z_{source} + Z_0} \frac{2Z_{load}}{Z_{load} + Z_0}}{1 - \frac{Z_{load} - Z_0}{Z_{load} + Z_0} \frac{Z_{source} - Z_0}{Z_{source} + Z_0}}$$

(3.1-43)

$$S_{\infty}(s,\omega) = \frac{Z_0 2 Z_{load}}{2 Z_{load} Z_0 + 2 Z_{source} Z_0}$$

(3.1-44)

$$S_{\infty}(s,\omega) = \frac{Z_{load}}{Z_{load} + Z_{source}}$$

(3.1-45)

The line just acts as a simple impedance divider between the source and the load impedance; it acts like a single lumped circuit element. Therefore it must be much shorter than 1/6 of the electrical length of a rising edge:

$$s \ll \frac{T_{rise}}{6\sqrt{L_{Line}C_{Line}}} \tag{3.1-46}$$

## 3.1.4 The influence of Vias

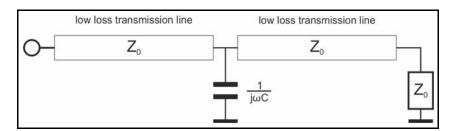

If connecting capacitive load to a transmission line, the reflection from the capacitive load can be calculated [2].

Figure 38: Transmission line with capacitive load

We assume that we deal with low loss transmission lines and that one branch of the transmission line is end terminated (there is no reflection). Its input impedance then equals to:

$$Z_0 = \sqrt{\frac{L}{C}} \tag{3.1-47}$$

We also assume that this branch is very long and so signals reflecting off from its far end will not contribute to the reflection from the capacitive load due to their flight time. At the capacitive load we then have a parallel combination of its impedance and Z<sub>0</sub>. We use the following equation for the reflection:

$$R_2(\omega) = \frac{Z_{load}(\omega) - Z_0(\omega)}{Z_{load}(\omega) + Z_0(\omega)}$$

(3.1-48)

Substituting  $Z_{load}$  with the parallel combination of the capacitive load and  $Z_0$  yields after simplifying:

$$R_C(\omega) = \frac{-j\omega C Z_0}{2 + j\omega C Z_0}$$

(3.1-49)

$$R_C(\omega) \approx \frac{-j\omega C Z_0}{2}$$

(3.1-50)

The latter equation looks like a differentiator (-sx). The -3dB point is reached at  $f=1/CZ_0\pi$ . Above this frequency the reflection is almost total.

For a signal transmitted through a capacitive load we assume again that both branches of the transmission line are long, as above, so that their effective impedance at the capacitive load can be calculated as in (xxx). We can now calculate the transmission coefficient:

$$T_C(\omega) = 1 + R_C(\omega) = \frac{1}{1 + \frac{j\omega C Z_0}{2}}$$

(3.1-51)

This is the equation of a first order low pass filter (1/(1+a s)) with time constant:

$$\tau = \frac{CZ_0}{2} {(3.1-52)}$$

The 10%-90% rise time of a step response can be estimated as:

$$T_{10-90}(step \ response) = 2.2 \frac{CZ_0}{2}$$

(3.1-53)

Now let us estimate the parasitic capacitance of a via:

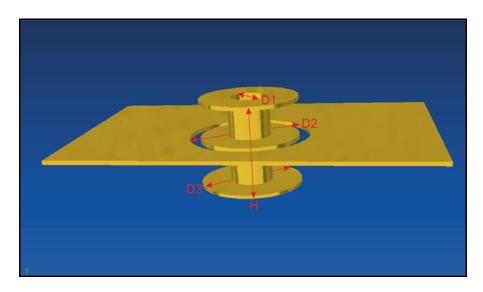

Figure 39: 3D-Model of a via (dielectric not shown)

The capacitance can only be predicted [2]. For exact calculation use a 3D-solver. The equation is:

$$C_{parasitic} = \frac{1.41\varepsilon_r H D_3}{D_2 - D_3} \tag{3.1-54}$$

where all measurements in inch and C<sub>parasitic</sub> in pF.

As an example we choose a 1.6mm PCB, a via hole diameter of 0.3mm, a via diameter of 0.6mm and a cutout diameter in the ground plane of 1.1mm. With an  $\varepsilon_r$  of 4.7 this gives a capacitance of about 0.51pF. This will effectively degrade the 10%90% rise time of a pulse by:

$$T_{10-90}(step\ response) = 2.2 \frac{0.51pF \cdot 50\Omega}{2} = 28.05ps$$

(3.1-55)

So the contribution of one via is rather small.

The inductance of a via is much more important. Since a via is a small structure it behaves like a limped circuit element. The inductance can be estimated from the inner diameter and the length of the via [2]:

$$L_{parasitic} = 5.08H \left[ \ln \left( \frac{4H}{D_1} \right) + 1 \right] \tag{3.1-56}$$

Where all measurements in inch and L<sub>parasitic</sub> in nH.

For our example above the parasitic inductance is  $L_{parasitic} = 1.2$ nH. This parasitic inductance increases the impedance of the current path to bypass capacitors and therefore degrades their effectiveness. At 100MHz the via has an Impedance of

about  $0.75\Omega$  and at 1GHz about  $7.5\Omega$ . If we have a rising edge with a  $T_{10-90}$  of 1ns the impedance is about 3.8Ω. Since a 1n ceramic capacitor has an ESR in this frequency range of below  $1\Omega$  the via together with the cap forms a 4:1 (!) voltage divider and the effectiveness of the bypass capacitor is down to \( \frac{1}{4} \).

#### 3.2 **Layout and Timing**

## 3.2.1 Calculation of timing requirements

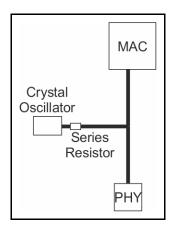

Having discussed the theory of transmission lines we now will discuss the layout techniques to improve signal integrity and reduce EMI. First of all to have a functional device, we must guarantee that the required timing of all integrated circuit is met. I will show that at an example design with a FREESCALE processor with integrated MAC and a DAVICOM PHY using an RMII interface. Now let us check the timing of the RMII interface. Since we use a crystal oscillator to source the clock for both, the PHY and the processor we must take care of the clock timing and the impedance of the clock line. The highest timing margin – since RMII is bidirectional using only one clock – can be achieved if the clock reaches the MAC and the PHY at the same time. Therefore a PCB microstrip structure called "balanced T" is used: Place the 50MHz crystal in the middle between the MAC and the PHY.

Figure 40: Balanced T structure

Put a series resistor for source impedance matching directly at the oscillator and route towards the MAC and the PHY as close as possible. Then route to the PHY and the MAC in a T-like structure keeping both traces as short as possible and of equal length. This guarantees that the clock arrives at the MAC and the PHY at the same time.

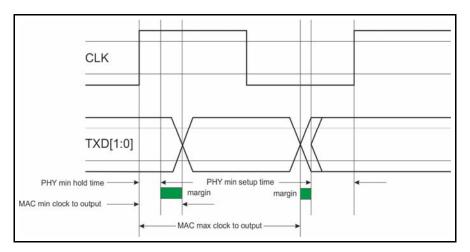

In order to meet the timing requirements all data and control lines that refers to the 50MHz clock should be not shorter than the clock line. No let us assume that the total clock trace length to the PHY and to the MAC is 2". We now try to match all traces that references to the clock to 2" as well. The timing requirements for TXD[1:0] referenced to the clock is shown in Figure 41. The maximum clock-to-output time for the MAC is 15ns. Since the minimum setup time for the PHY is 4ns we have a margin of

1ns for signal rise and fall time as well as the flight time on the PCB trace. For a 2" transmission line on FR4 the propagation delay is about 180ps/in therefore for a 2" trace the propagation delay is about 0.36ns. So even a 3" data trace would keep the setup timing within its margins. The minimum hold time of the PHY is 2ns and the minimum clock-to-output time for the MAC is 4ns. The margin for the hold time therefor is 2ns and each inch of data trace would even increase the margin. Since the margin for the hold time is larger than for the setup time one could think about making the clock traces longer than the data traces.

Figure 41: Timing requirements for TXD[1:0]

Unfortunately the clock-to-output timing of the RMII interface of the selected DAVI-COM PHY (DM9161C) is not specified in its datasheet.

# 3.2.2 Layouting traces on the PCB

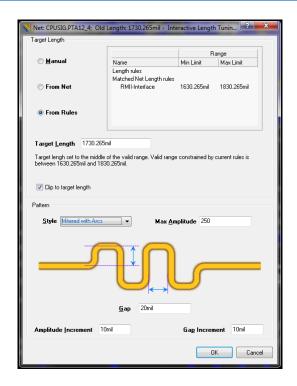

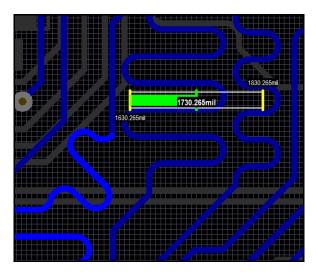

Since we need length matching for signals use a layout system which supports that. My layout system lets me adjust the length matching parameters and semiautomatically lets me length match a trace with a meander-like structure.

Figure 42: Adjustment of length matching parameters in layout system

You should use arcs for mitering since rectangular mitering alters the cross section of the trace and therefore will introduce impedance "bumps". For semi-automatic length matching the system tries to match to a target length and shows a bargraph that follows a length-matching-rule.

Figure 43: Semi-automatic length matching of a PCB trace.

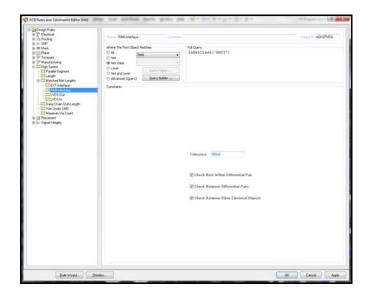

The length matching rule must be adjusted to the required timing margin from the timing calculation above. My system allows to define net classes for signals and I can then define a rule for such a net class. The following figure shows a length-matchingrule with a tolerance of 100mil for a net class "RMII-Interface".

Figure 44: Length matching rule for the RMII interface.

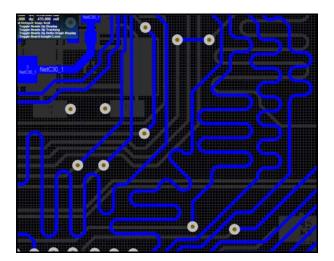

After length matching the traces in the layout check carefully for crosstalk possibilities. Avoid paralleling of traces over a long distance and also keep other traces away from clock traces at least 3 times of the trace width. Also try to keep the number of vias in a trace low since vias are impedance discontinuities and introduce an additional delay.

Figure 45: Layout on one Layer after length match-

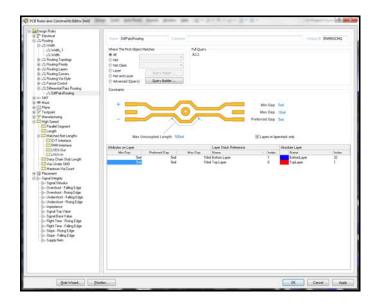

For the differential TX+/- and RX+/- pairs between PHY and magnetics you must also define routing rules.

Figure 46: Routing rule for differential pair routing.

You should keep the uncoupled length as small as possible and obey the gap rule.

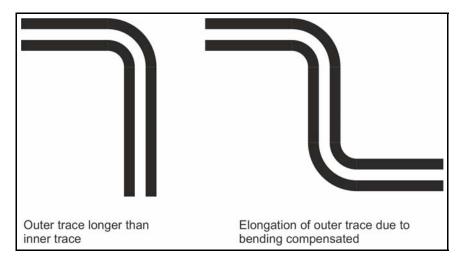

A differential pair also needs to match within the pair. The difference in length between both traces must be kept as small as possible. If bending the differential pair in one direction the outer traces become elongated. So for compensation you should bend the differential pair into the opposite direction.

Figure 47: Compensation of length mismatching in differential pairs

# 3.2.3 Layer stack, VCC and GND planes in the layout

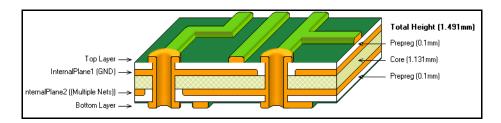

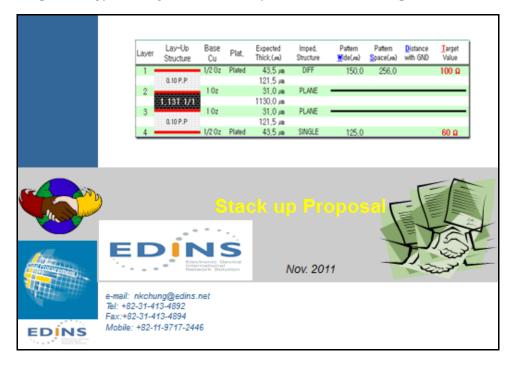

You should use at least a 4-Layer design since a GND-plane is mandatory. Also the design should be impedance-controlled and the required dimensions should be calculated by means of a 2-D or 3-D solver. This can be done in most cases by the PCB manufacturer.

Figure 48: Typical 4-Layer Stack of an impedance controlled design

Figure 49: Layer stack calculation provided by the PCB manufacturer

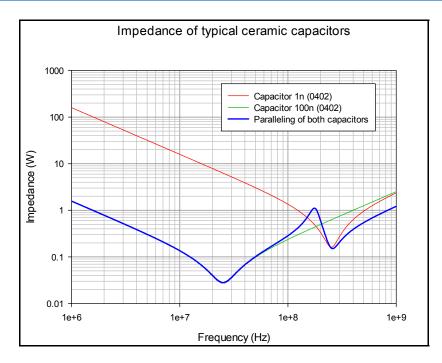

The impedance from the power or ground plane to the supply pads of a device should be kept as low as possible. For a low impedance supply bypassing, use a combination of different capacitors like 100n and 1n.

Figure 50: Paralleling of bypass capacitors of different value gives a low impedance over the whole frequency range

To decrease the influence of the via inductance use two or three vias to connect the bypass capacitors to the plane instead of one. This is also true for large bulk capacitors, sincethe vias must be capable to carry the current there. Small capacitors must be placed very close to the supply pad to keep the high frequency impedance low. Larger capacitors or bulk capacitors can be placed further away.

Figure 51: Routing of a bypass capacitor

Do not use Z5U dielectric material capacitors since they have worse aging, temperature coefficient and capacity loss due to DC biasing, use X7R or X5R.

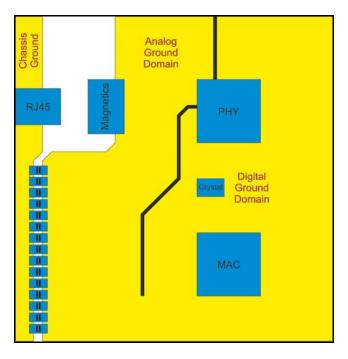

Since most PHYs have an analog and a digital domain you should avoid current passing from the digital domain into the analog domain. This can be done by slotting the ground plane but leave a broad tab as connection between digital and analog ground plane at one point. Also a connection between chassis ground and analog ground may be beneficial (or not! You have to check that in the EMI lab). If using a capacitive coupling between analog ground and chassis ground, be aware that you need several capacitors of different capacity to guarantee a low impedance connection over the whole frequency range. This depends on your hardware, as well as on the enclosure of the device.

Figure 52: Ground plane design in a typical Ethernet application

## 3.2.4 Where to put the termination resistors

Ethernet uses parallel termination. That means that the termination network has to be placed close to the RX pins of the PHY. Normally two 49R9 resistors which are connected together are used. The midpoint (the connection between the resistors) is then ac-terminated to GND by means of a 100n capacitor. This terminates both lines independently. If you would use only a single  $100\Omega$  resistor between both lines and if you have a skew between the RX+ and the RX- signal then the  $100\Omega$  resistor would create two artifacts during the skew interval (crosstalk from RX+ to RX- and vice versa; see Dr. Howard Johnson:

http://www.sigcon.com/Pubs/edn/DifferentialTermination.htm). Since many PHYs use a differential current source as transmitter the transmit lines need  $50\Omega$  pullups to VCC. Place those resistors as close as possible to the TX pins of the PHY. Placing all termination networks close to the PHY helps to reduce the return loss.

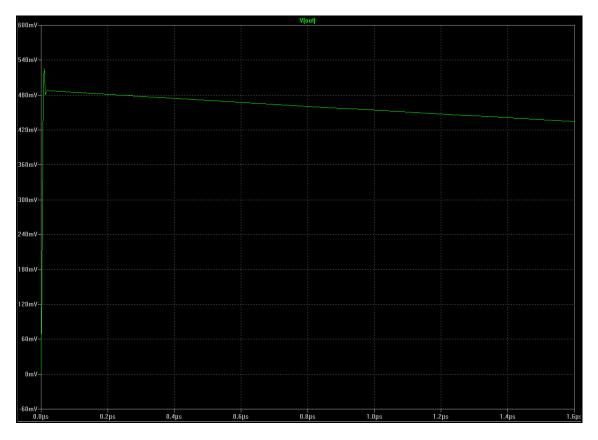

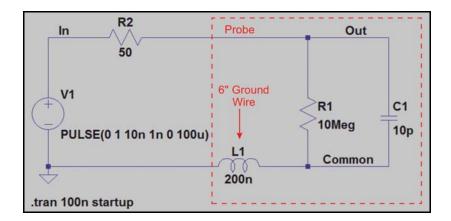

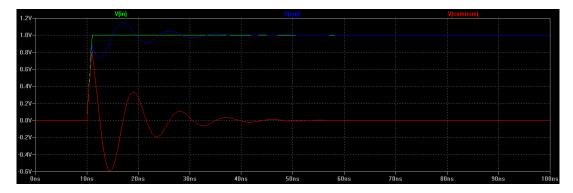

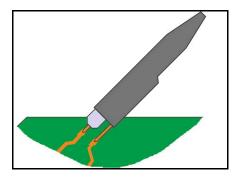

## 3.2.5 Miscellaneous